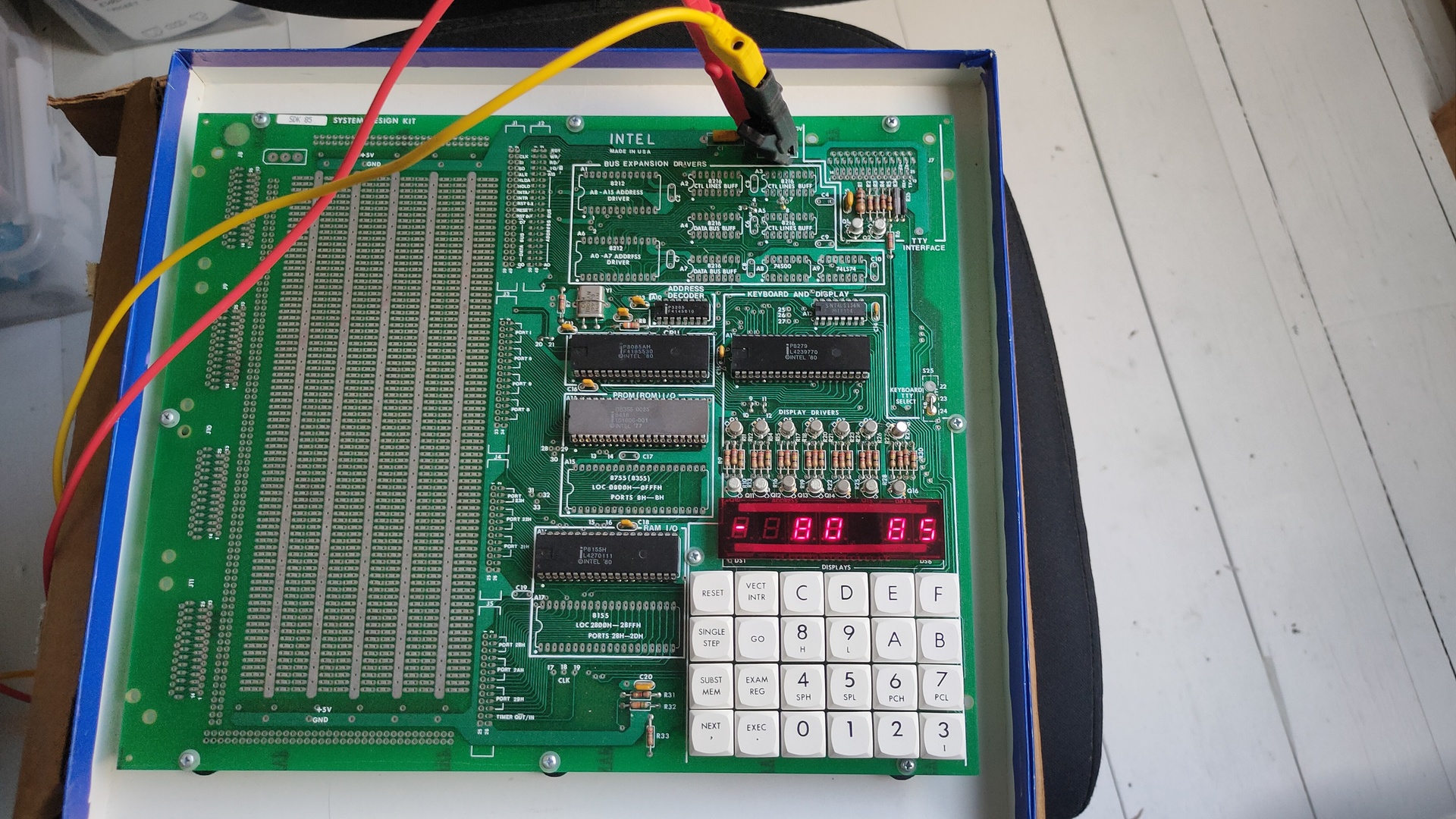

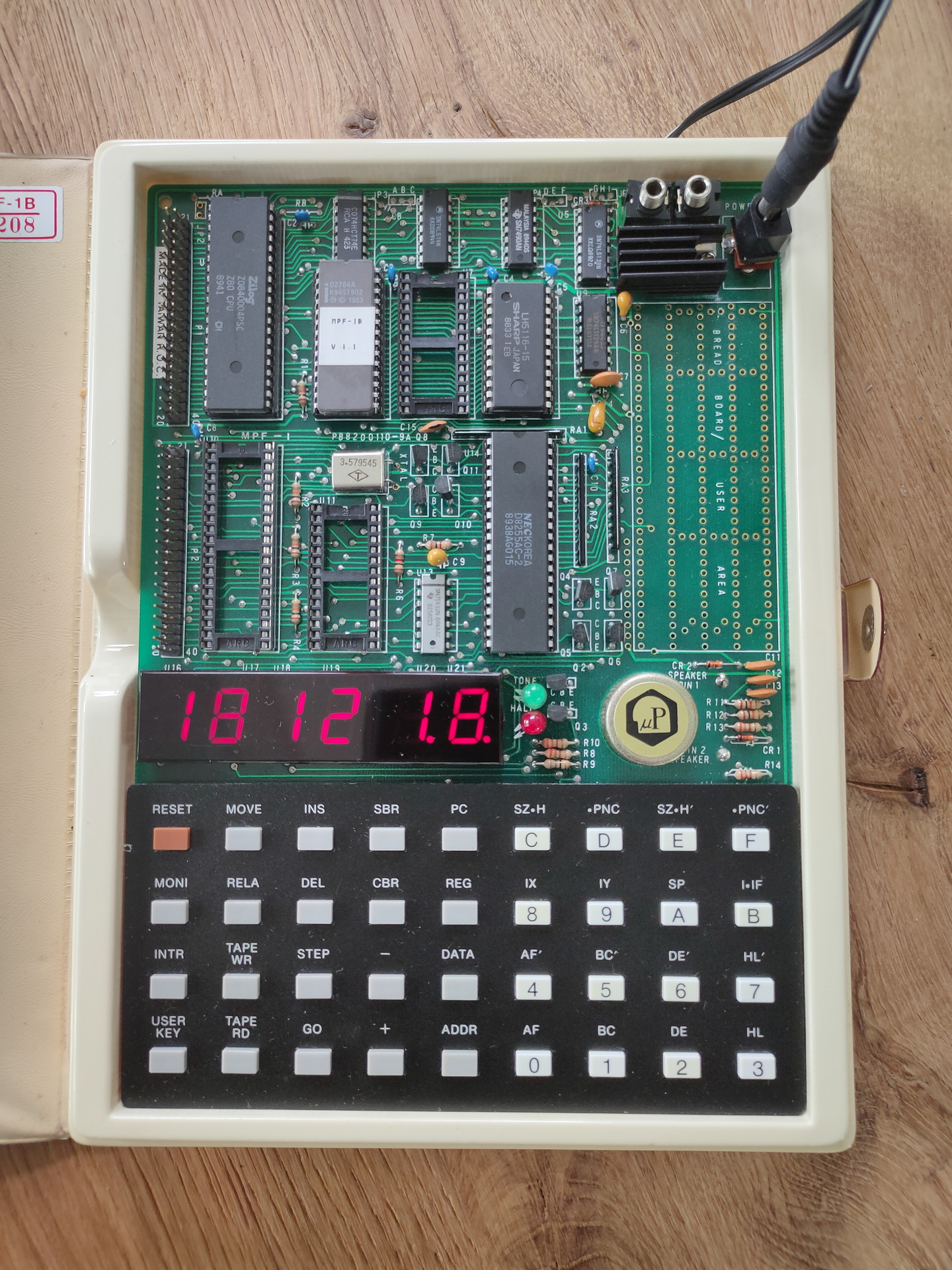

There are a lot of old develop boards for all kinds for cpu’s.

These where build to learn machine code programming. Mostly made in the 80’s, and based on populair cpu’s at that time.

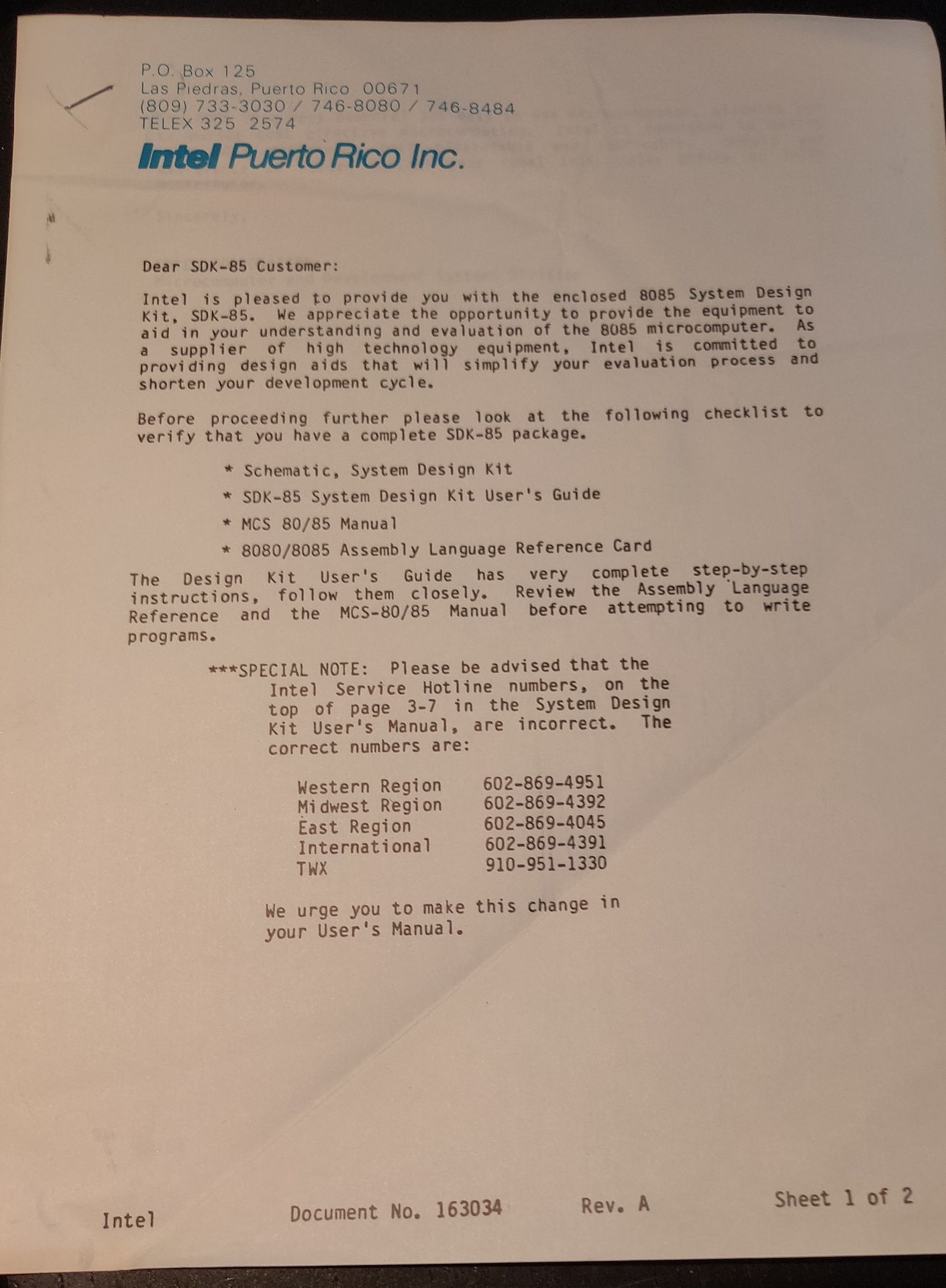

I own a some of these SDK’s (System Design Kits)

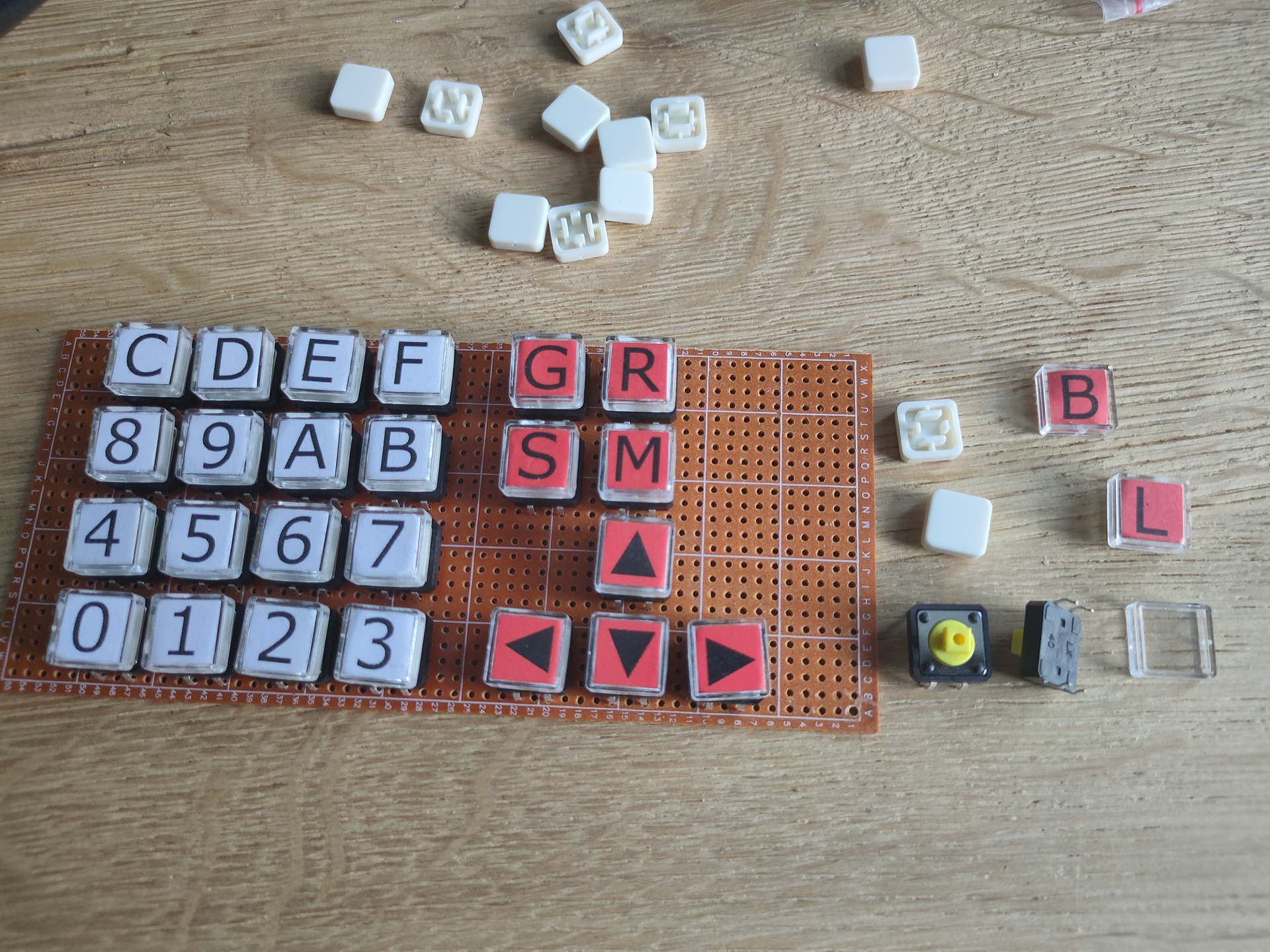

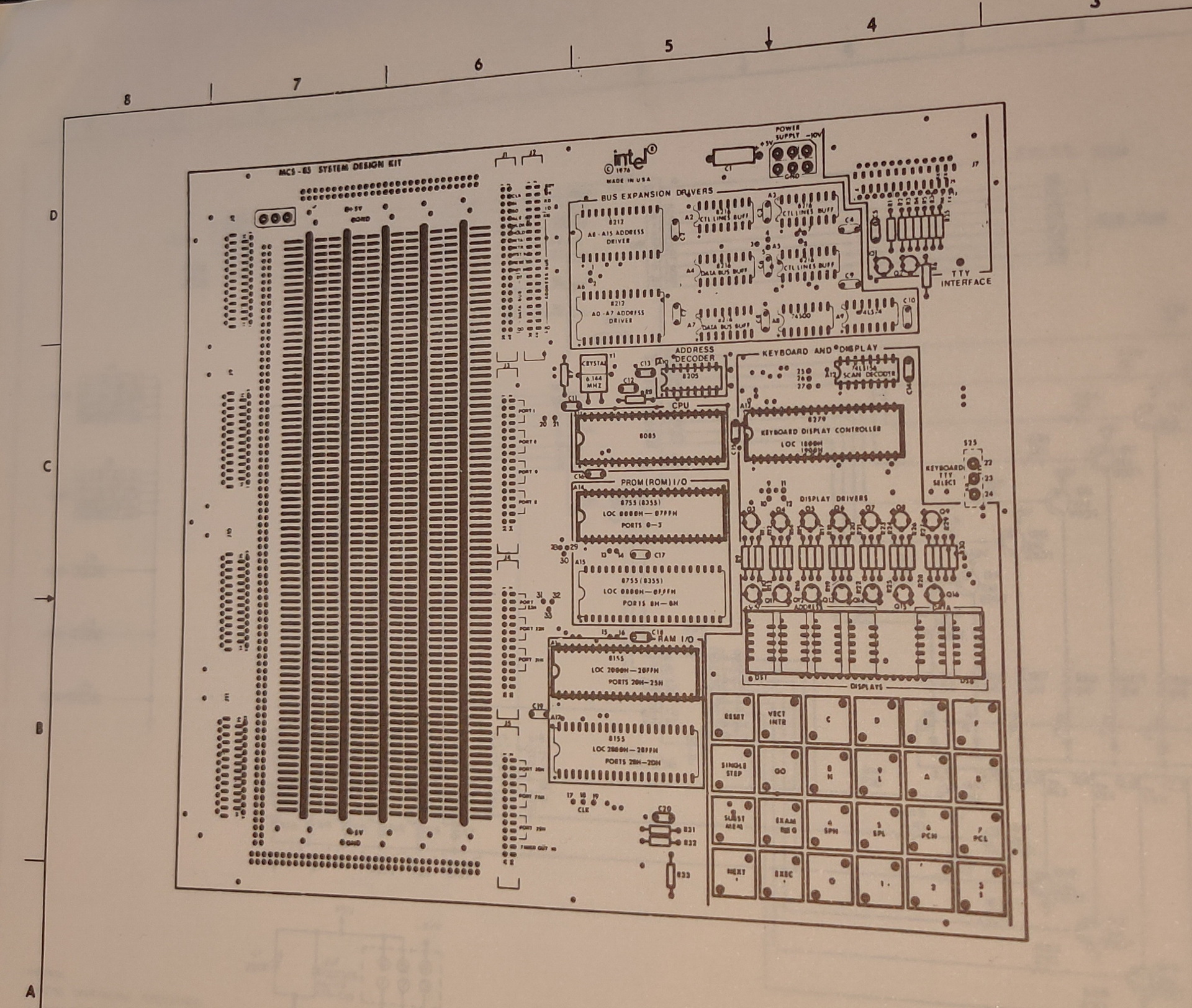

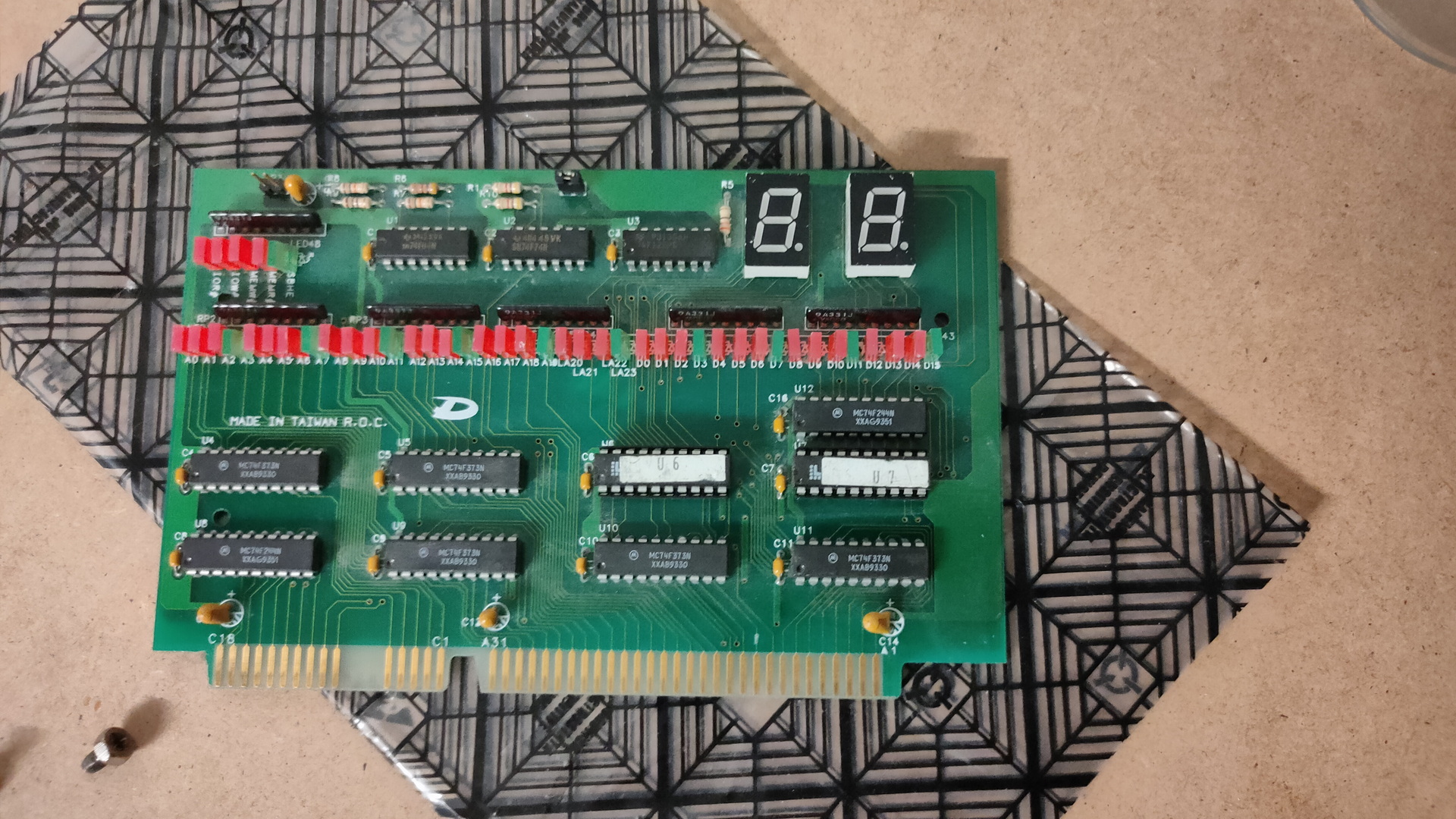

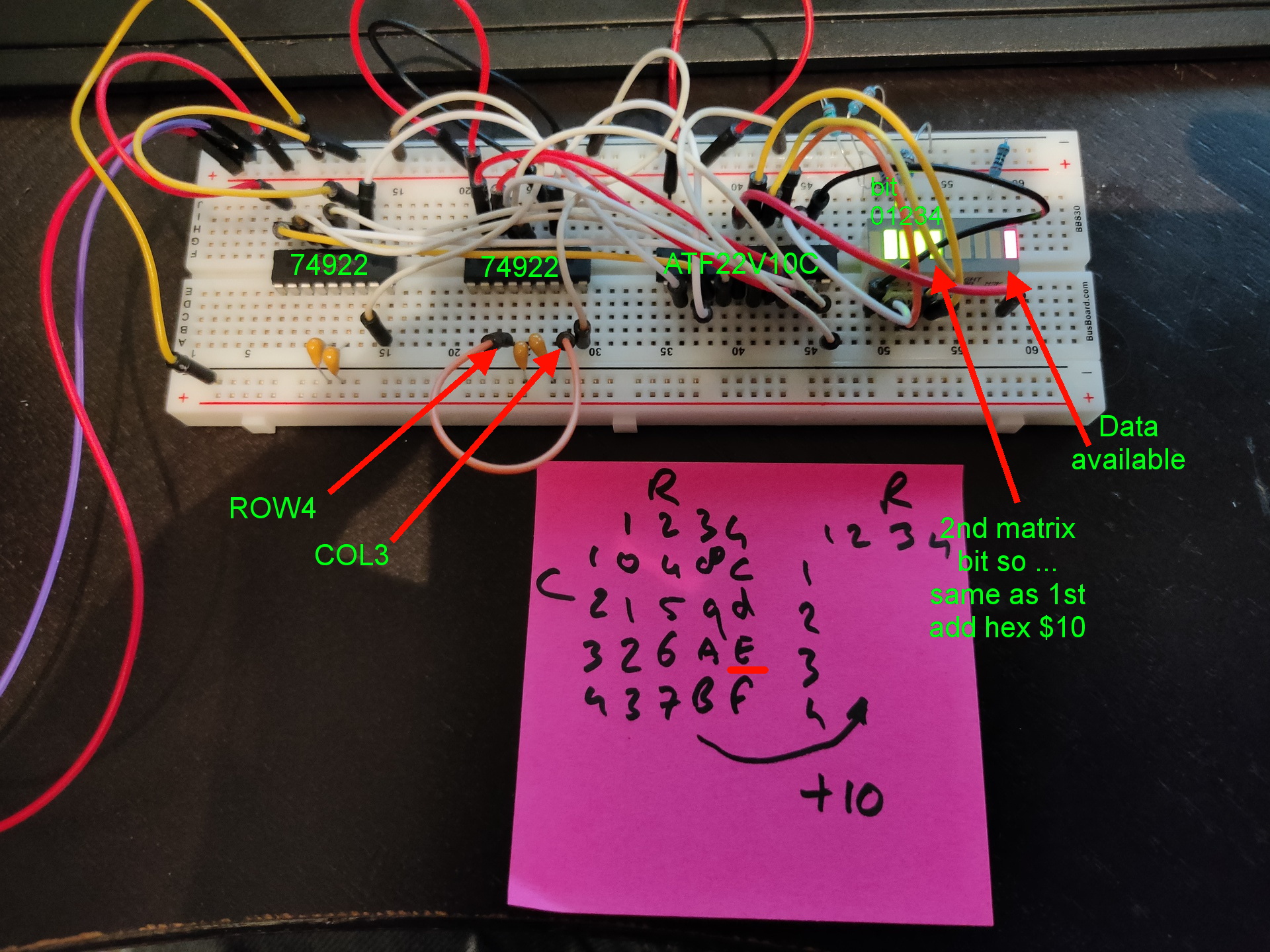

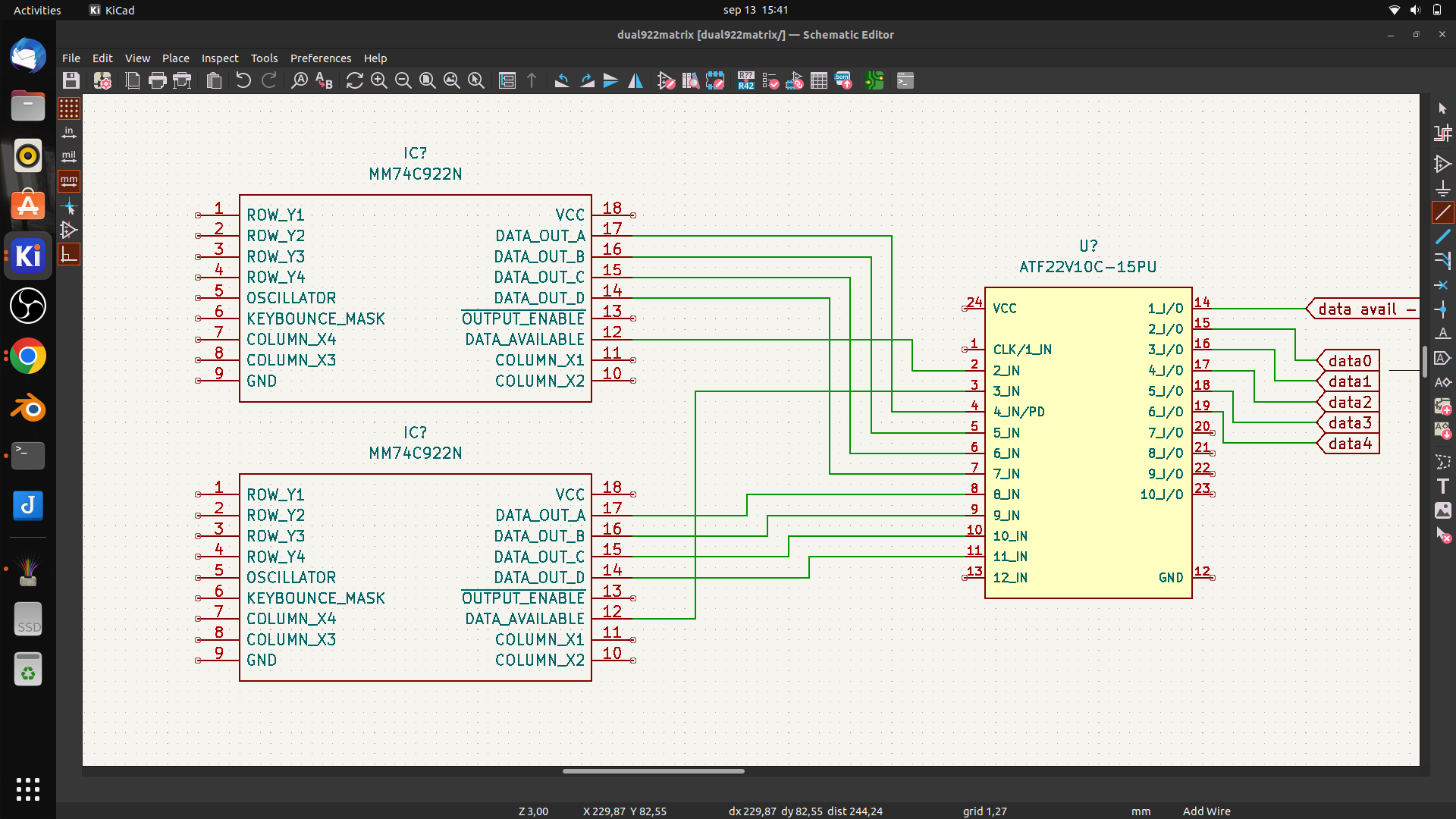

Most of these use a keyboard scanner which is also connected to 7 segment displays.

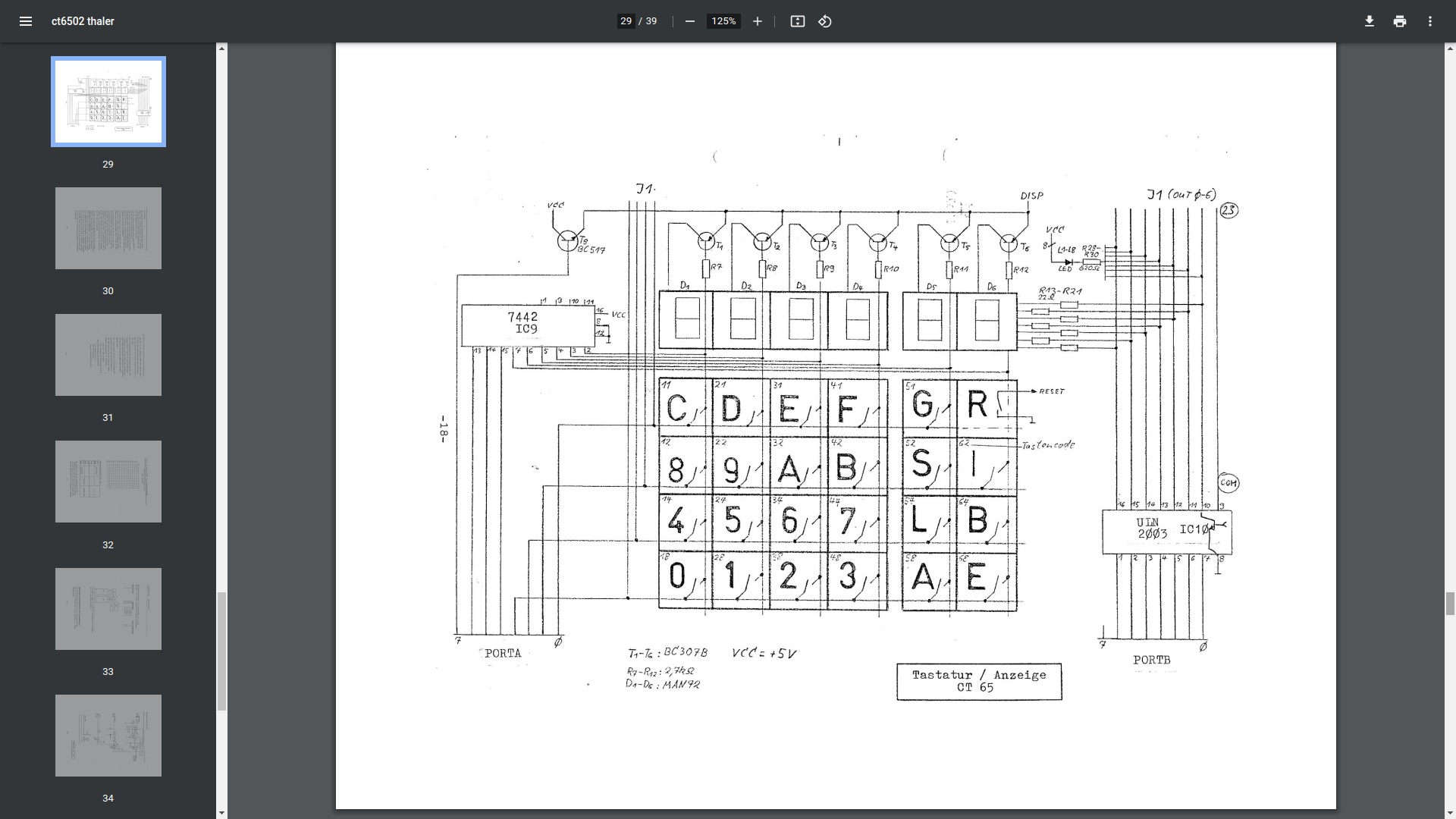

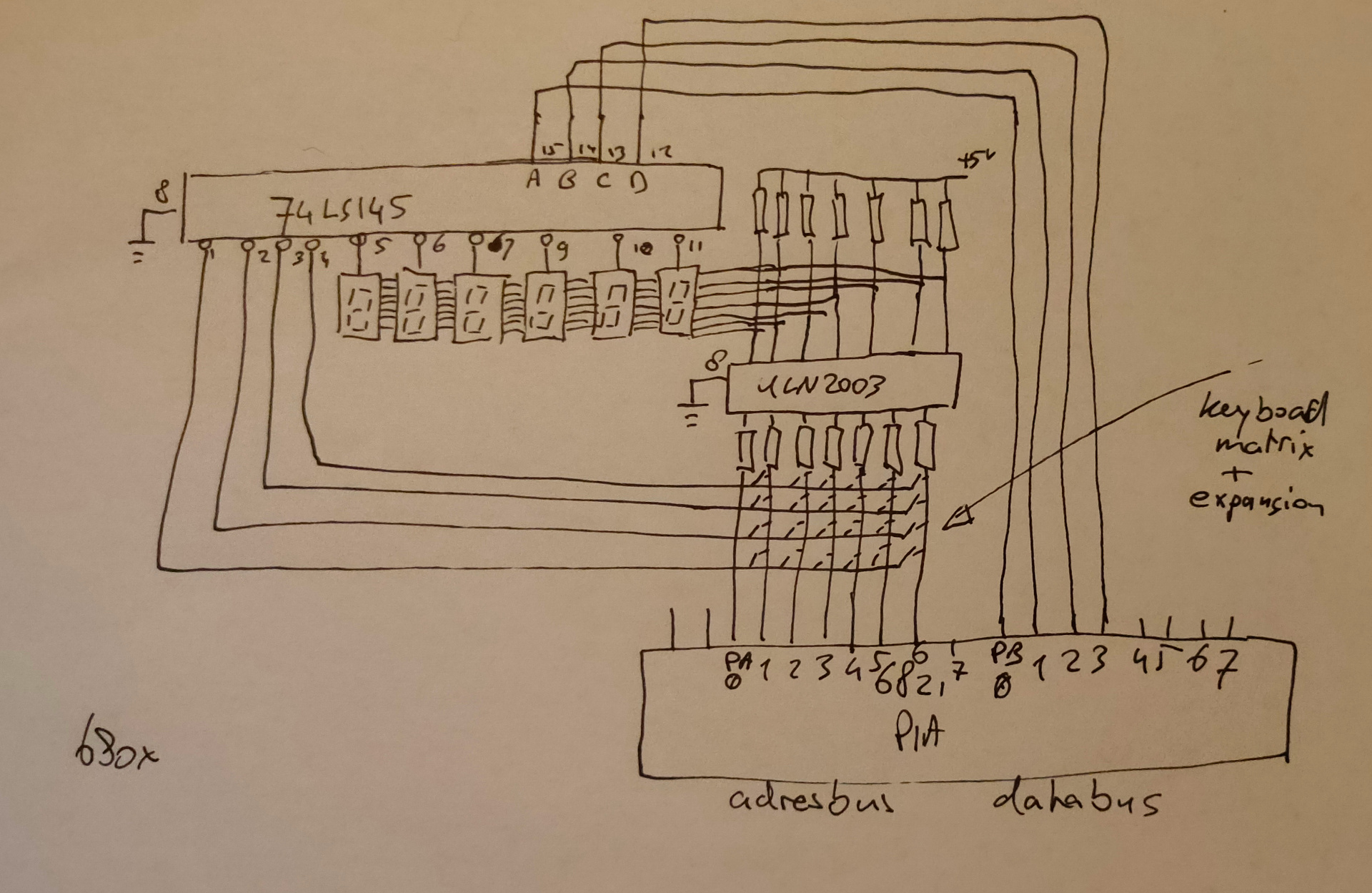

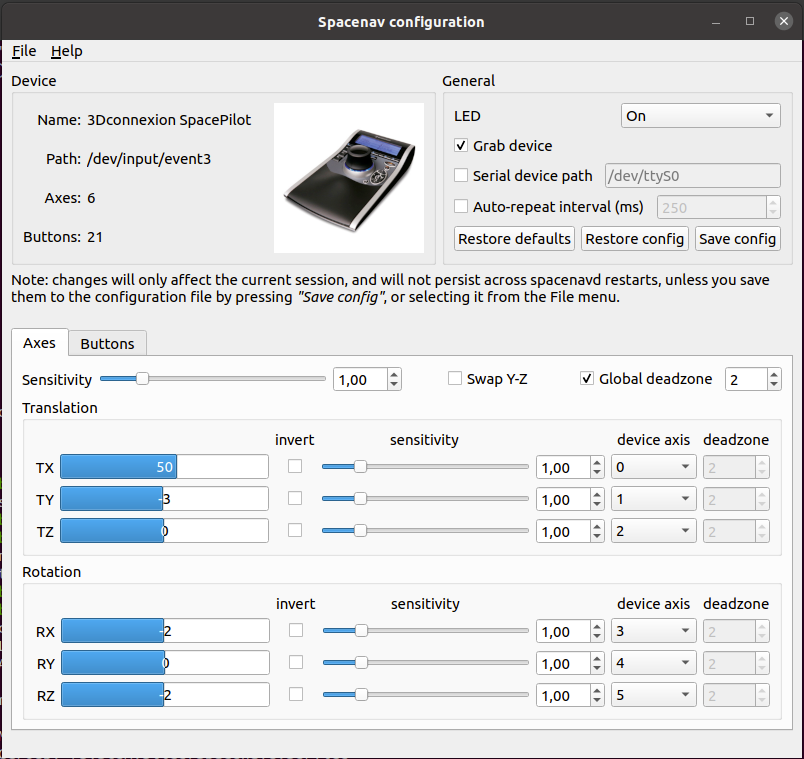

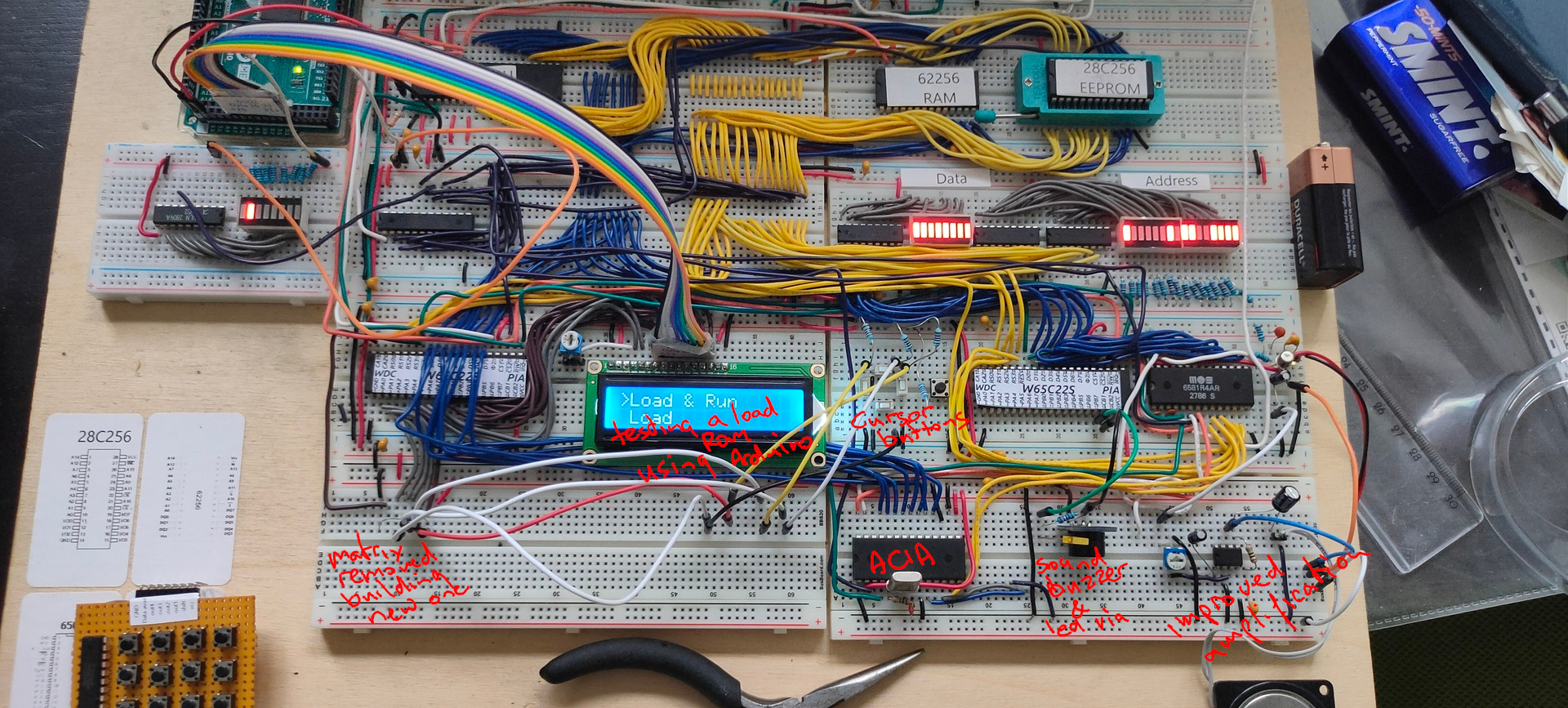

The way they work is practically the same. There is a VIA or PIA. Versitile interface adaptor, or Peripheral interface adaptor. These have two times 8 bits to control devices.

When using 4 bits and convert these to 16 lines by using a 75ls145 for example. If you put a counter on those 4 bits, you sequently activate 1 of 16 lines. These lines you can use to scan a keyboard matrix OR display a character on a 7 segment display. These display’s won’t hold the data (and show the character) when not activated. The trick is to update de display fast enough so you don’t see the flickering on/off.

Activate a line and read a byte with the VIA = Reading keyboard row

Activate a line and write a byte with the VIA = Display on a segment

These VIA/PIA’s where made with specific timings to match the CPU.

6522/6820/8255

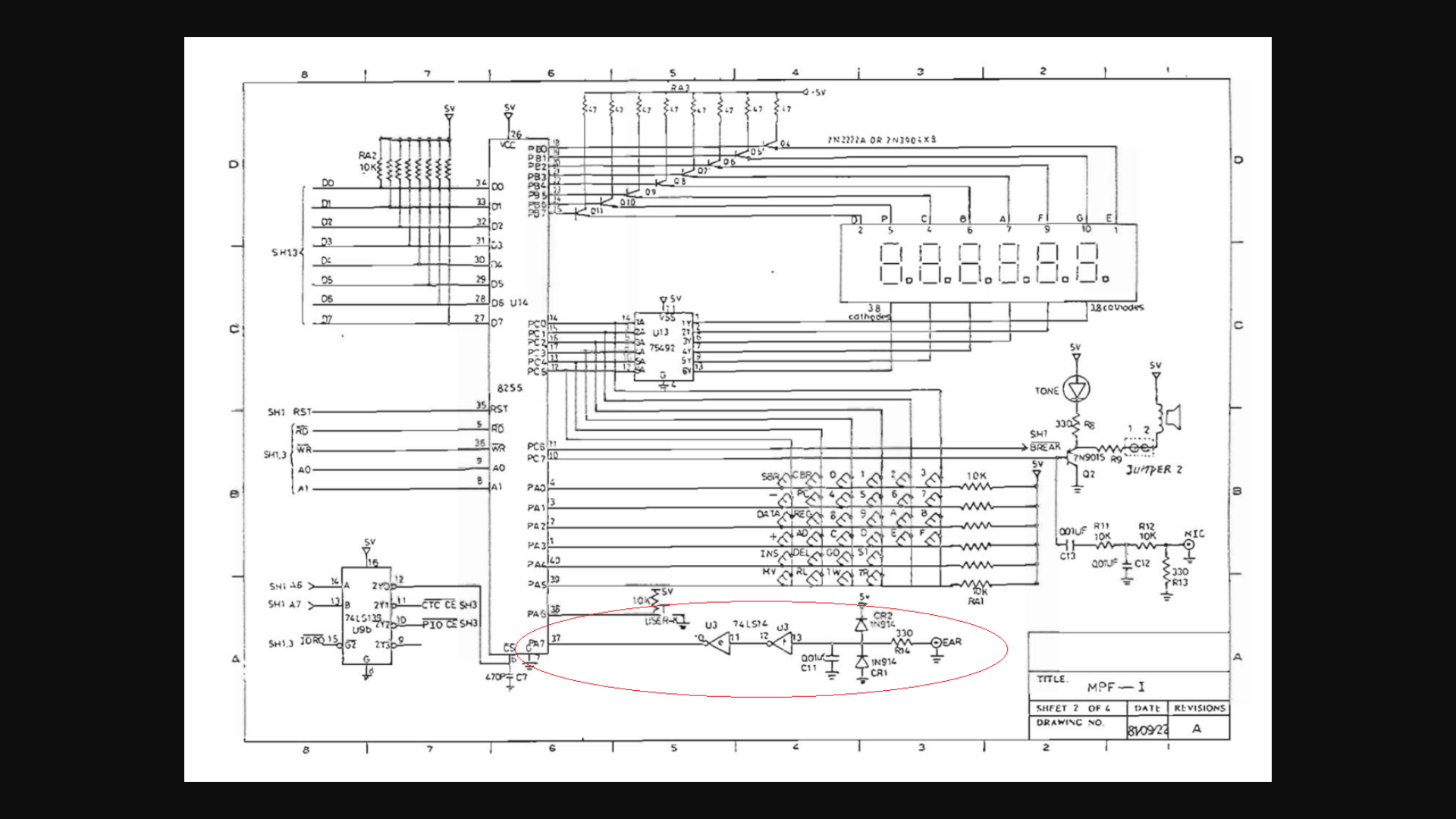

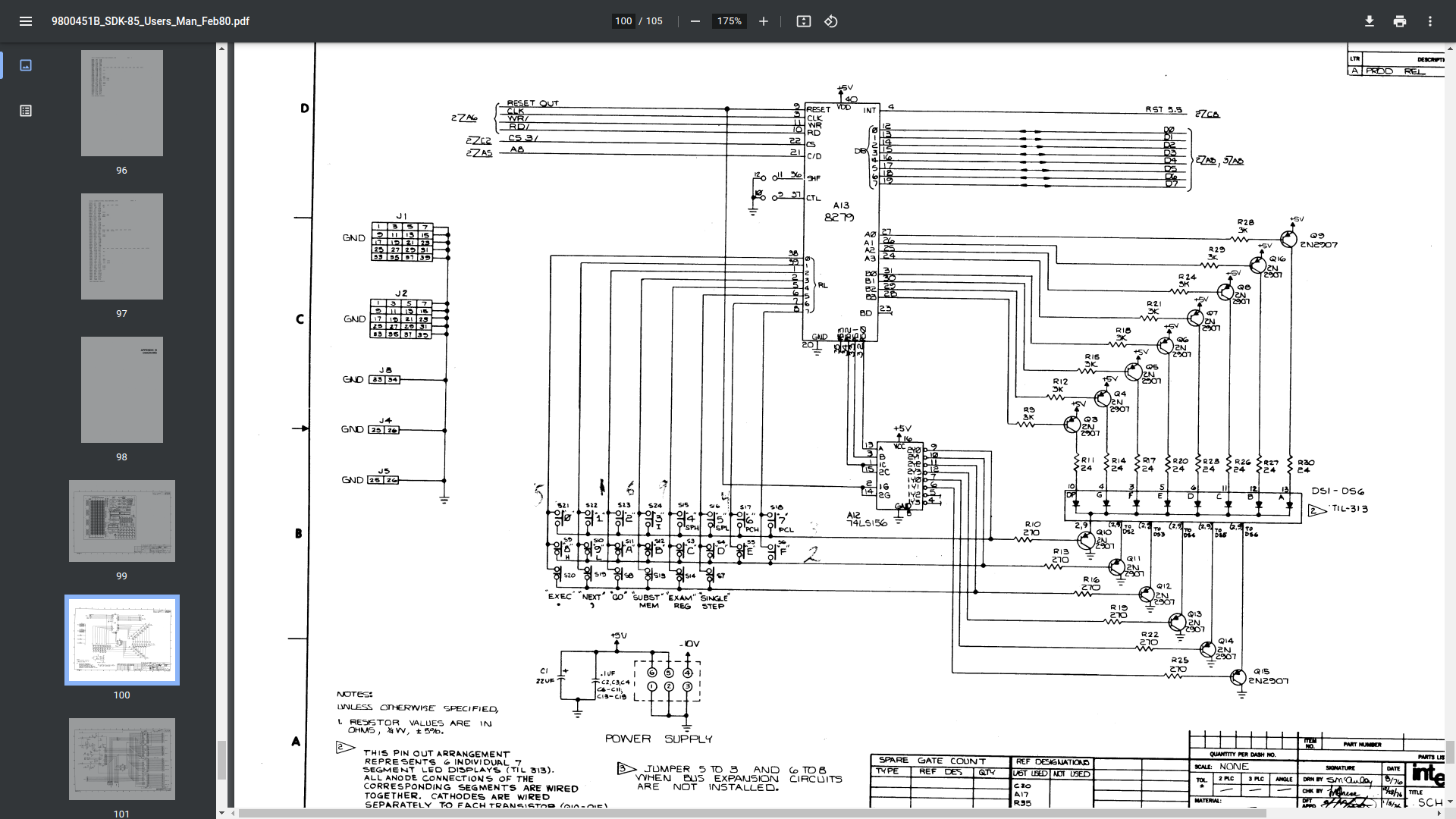

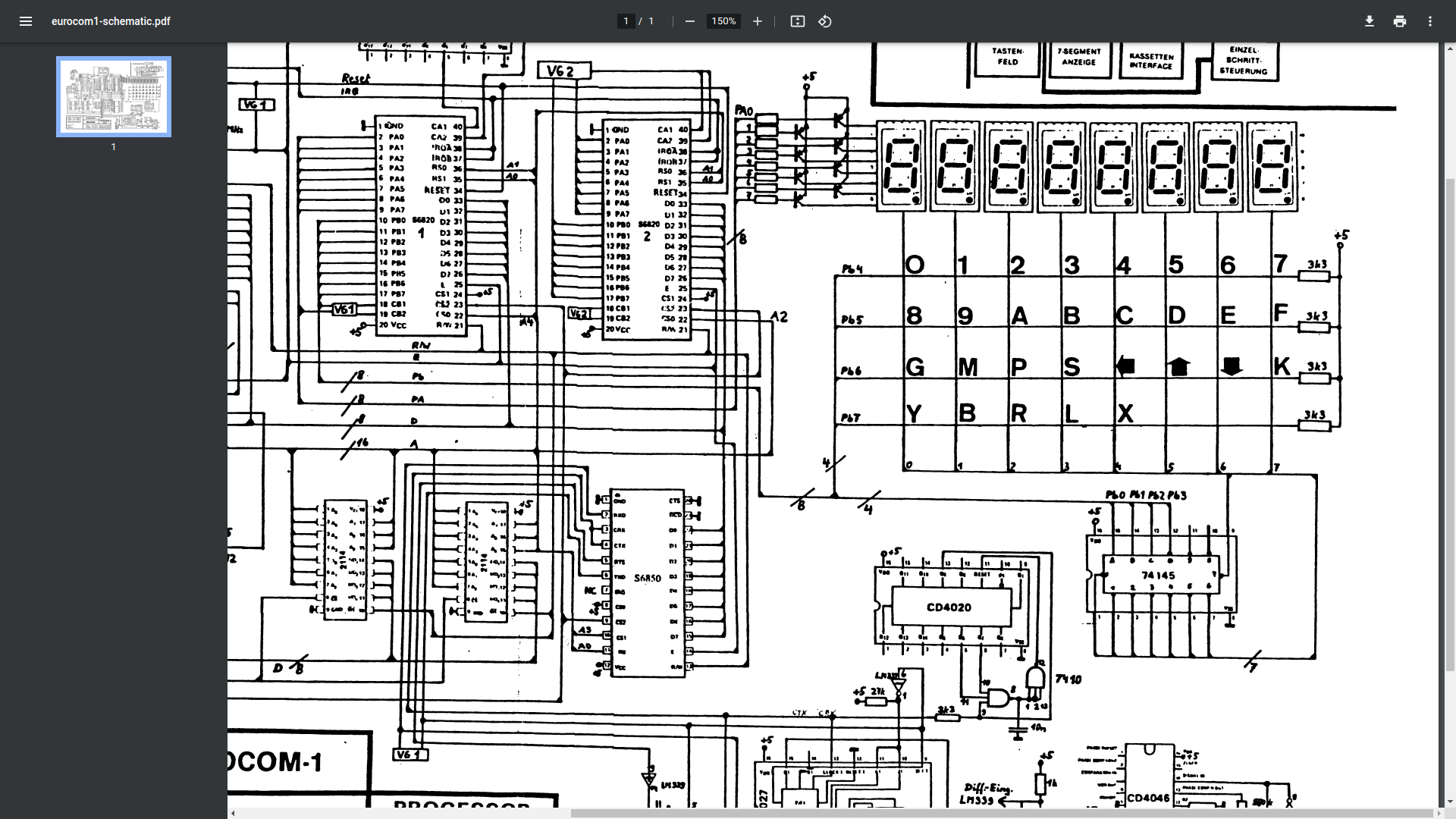

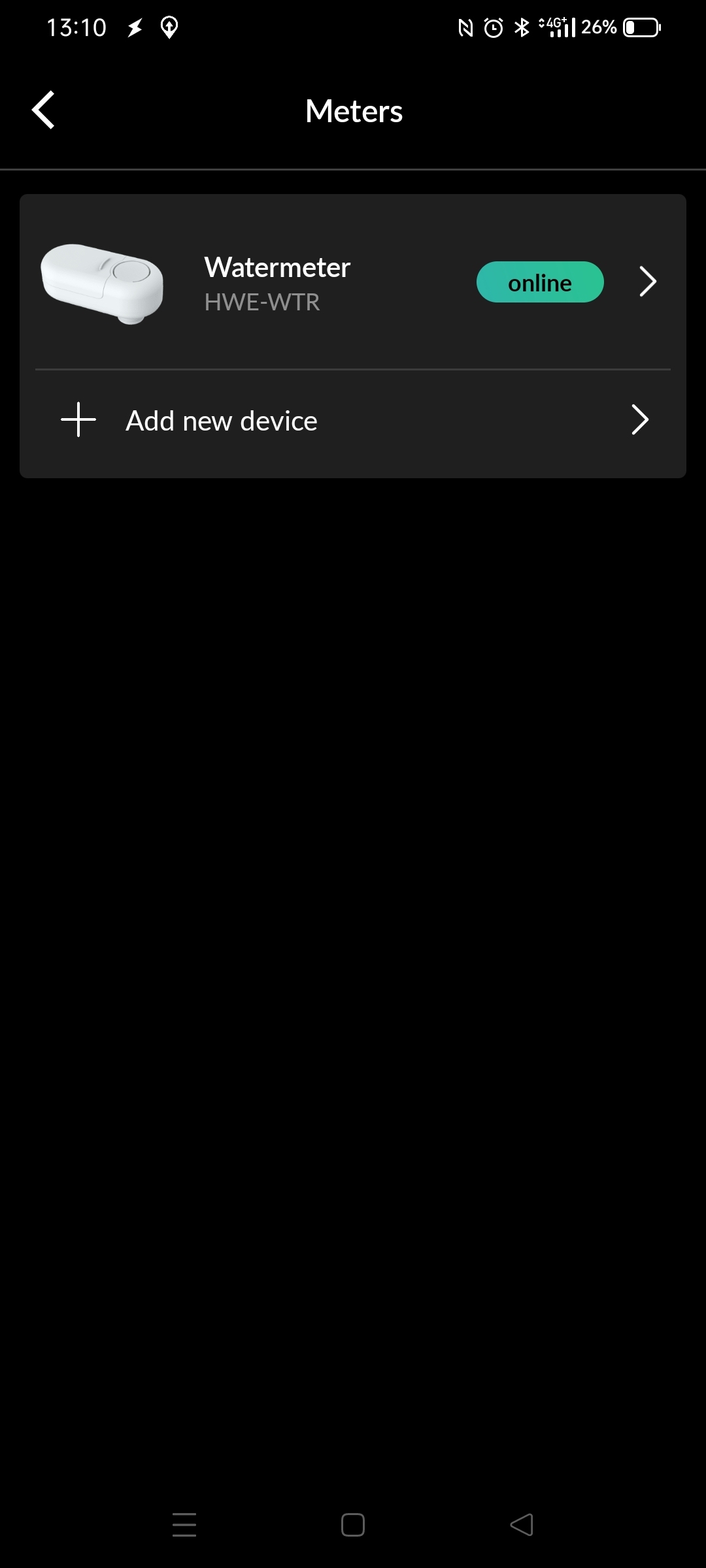

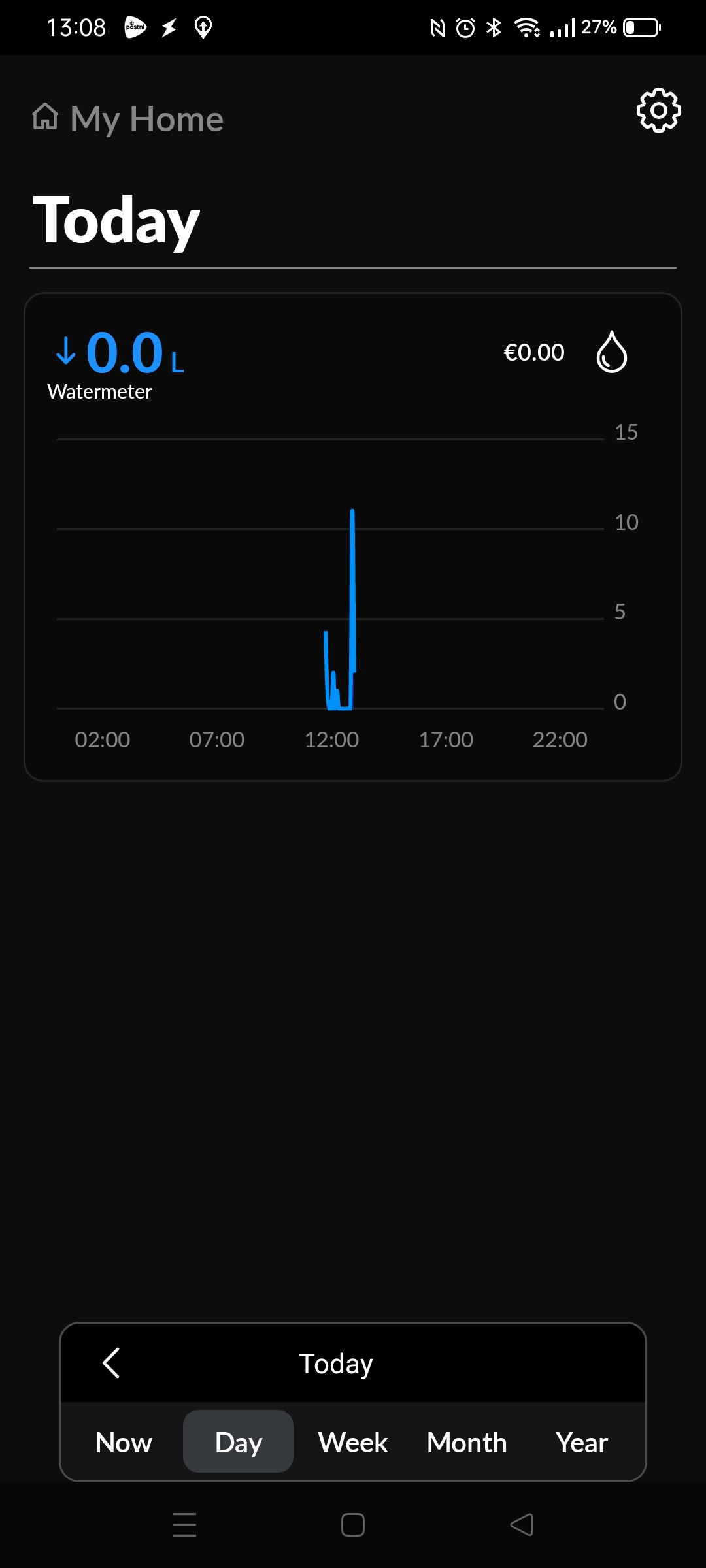

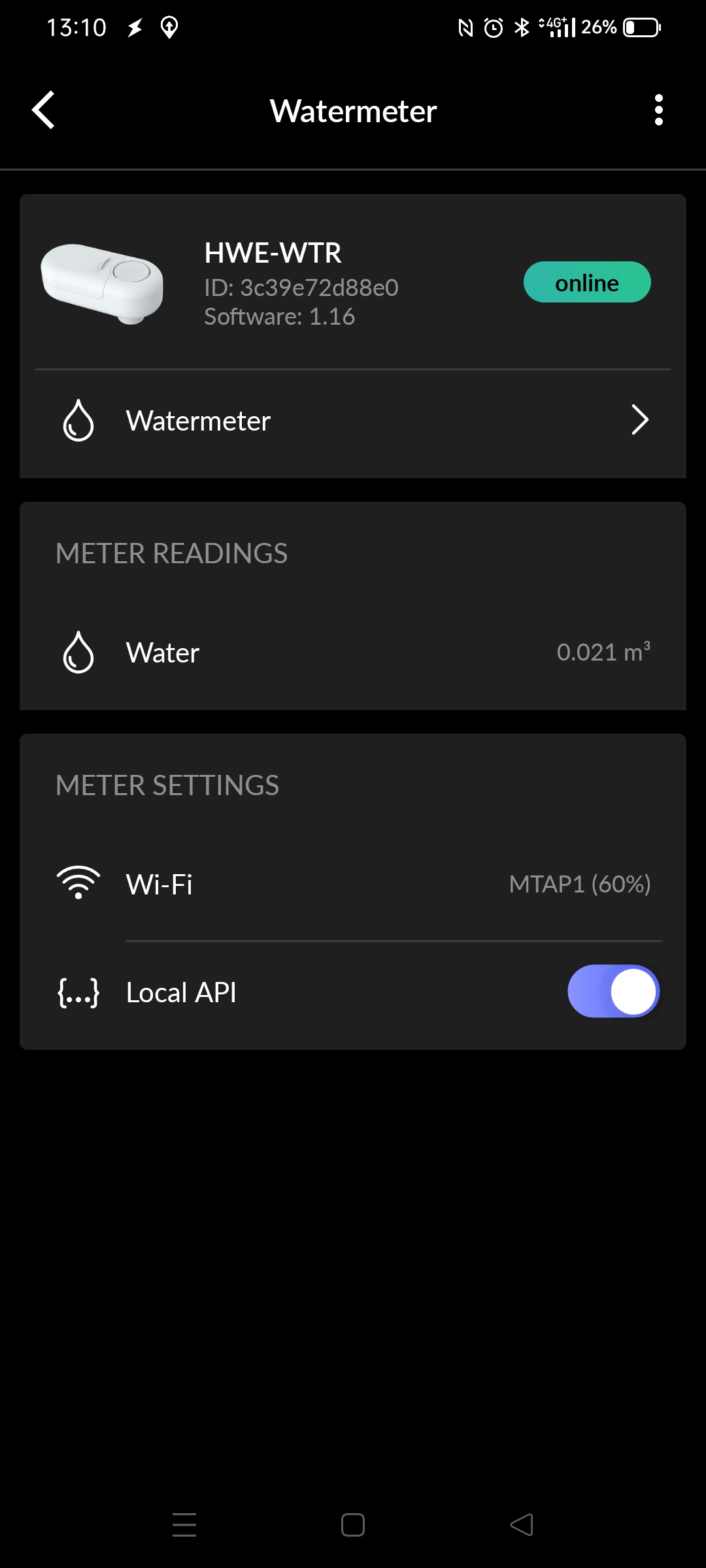

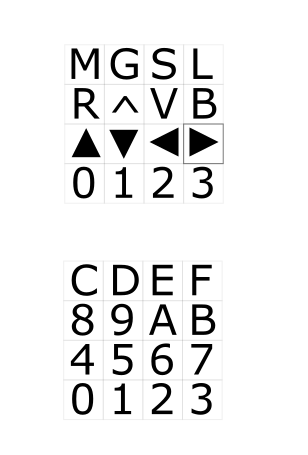

Below you see some different implementations of these keyboard/display combo’s

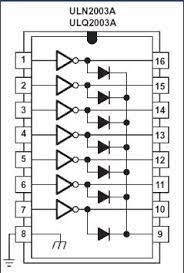

When looking at the 8085 version you see transistors being a ULN2003 is a chip with those transistors/amplification enclosed.

It doesn´t draw much current from the bus, and diodes protect the way the current flows.